芯片产业 - 常见流程和术语

角色Foundry,在集成电路领域是指专门负责生产、制造芯片的厂家Fabless,是Fabrication(制造)和less(无、没有)的组合,是指“没有制造业务、只专注于设计”的集成电路设计的一种运作模式,也用来指代未拥有芯片制造工厂的IC设计公司;通常说的IC design house(IC设计公司)即为Fabless。晶圆Wafer,一片完整的晶圆,由纯硅(Si)构成。一般分为6英寸、8英寸

本文所有信息均来自网络

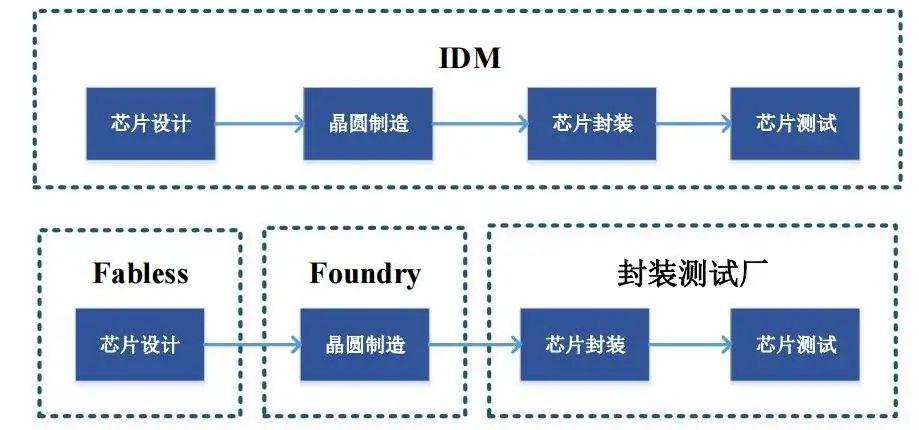

角色

Foundry,在集成电路领域是指专门负责生产、制造芯片的厂家

Fabless,是Fabrication(制造)和less(无、没有)的组合,是指“没有制造业务、只专注于设计”的集成电路设计的一种运作模式,也用来指代未拥有芯片制造工厂的IC设计公司;通常说的IC design house(IC设计公司)即为Fabless。

晶圆

Wafer,一片完整的晶圆,由纯硅(Si)构成。一般分为6英寸、8英寸、12英寸规格不等

die,Wafer上的一个小块,就是一个晶片晶圆体,学名die,封装后就成为一个芯片(chip)

wafer首先经过切割,然后测试,将合格的die取下

晶圆等级

原装片:三星、现代等厂商,生产出来的晶圆是按容量分等级的,高于93%容量的晶圆被称为A级品,简称A片,原厂封装并提供质保,品牌闪存一般使用此类芯片。

白片:低于93%容量的晶圆被称为Downgrade

Flash,不再打上原厂的雷刻标识,由一些小封装厂进行加工。其中相对足量,稳定使用的一般称之为白片。价格一般为A级品的7成至8成。

黑片:待封装芯片中容量严重不足、质量难以保障的为黑片。另外部分不良商家回收废旧闪存芯片,打磨而成的闪存芯片一般也称之为黑片。

工艺和阶段

CP (Chip Probing 芯片/晶片+测试/探测): 顾名思义,测试芯片的电性参数。测试的是晶圆中的每一个芯片(die),目的是剔掉次品以减少后续封装的成本

WAT (Wafer Acceptance Test 允收晶片/圆测试): 对专门的测试图形 (test key) 的测试,通过电参数来监控各步工艺是否正常和稳定

FT (Final Test 出厂测试): 对封装好的芯片进行测试。通常测试项比CP要少得多,因为之前已经测过了

Tape Out, 流片(投片)

Mask 芯片掩膜版/光罩,是用来制造集成电路各个层次的母版,比如说N阱,有源区,多晶硅,金属1,通孔,金属2.... 金属10...... 这些工艺层。 芯片是以上各工艺层精密叠加的产物。

Full Mask是“全掩膜”的意思,即制造流程中的全部掩膜都为某个设计服务

MPW(MulTI-Project Wafer, 多项目晶圆),是将多个具有相同工艺的集成电路设计放在同一晶圆片上流片加工服务,每个设计品种可以得到数十片芯片样品,用于产品研发阶段的实验和验证测试。

流片的过程和成本

来自:流片需要经历哪些过程,为什么贵,为什么正式生产就便宜了?MASK贵在哪? - 知乎

Foundry的报价都是根据工艺和投片的量,给出单层mask价格。

费用=Mask制版费+N*单片晶圆成本。也就是说成本大约分为两类,

1是MASK成本,大约30-50万美元。

2是Wafer成本,就是晶圆成本,每片晶圆在1500-2000美元左右。

刻蚀在28nm前的成本是低于光刻的,而目前14、7nm因为多为离子刻蚀

此外还有测试成本和封装成本

三大EDA厂商

Synopsys、Cadence、Mentor

主流IP供应商

ARM、eMemory、Synopsys、Cadence

芯片种类

ASIC: 专用集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路

MCU: 微控制单元(Microcontroller Unit;MCU) ,又称单片微型计算机(Single Chip Microcomputer )或者单片机,是把中央处理器(Central Process Unit;CPU)的频率与规格做适当缩减,并将内存(memory)、计数器(Timer)、USB、A/D转换、UART、PLC、DMA等周边接口,甚至LCD驱动电路都整合在单一芯片上,形成芯片级的计算机,为不同的应用场合做不同组合控制

DSP芯片:也称数字信号处理器,是一种特别适合于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理算法

SoC(System on Chip)即片上系统,是智能设备的大脑,是将系统关键部件集成在一块芯片上,可以实现完整系统功能的芯片电路. 数字IC从基于时序驱动的设计方法,发展到基于IP核复用的设计方法,并在SOC设计中得到了广泛应用。在基于IP核复用的SoC(System on Chip的缩写,称为系统级芯片,也有称片上系统)设计中,片上总线设计是最关键的问题,

RISC是英文Reduced Instruction Set Computer的缩写 ,就是“精简指令运算集”,

CISC就是“复杂指令运算集”

工作寿命试验 (OLT)

新产品下线NTO new tape out

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)